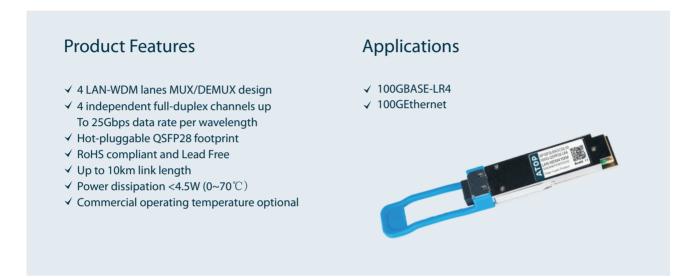

# 100Gb/s QSFP28 LR4 Transceiver

# APQP2LRACDL10A

# 103Gb/s QSFP28 LR4 Transceiver

APQP2LRACDL10A

#### **Product Selection**

| Part Number    | Operating Case temperature      | DDMI |

|----------------|---------------------------------|------|

| APQP2LRACDL10A | Commercial(0~70 <sup>°</sup> C) | Yes  |

#### **Regulatory Compliance**

- ESD to the Electrical PINs: compatible with MIL-STD-883 Method 3015

- ESD to the Duplex LC Receptacle: compatible with EN 61000-4-2

- Immunity compatible with EN 61000-4-3

- EMI compatible with FCC Part 15 Class B

- Laser Eye Safety compatible with FDA 21CFR 1040.10 and 1040.11 IEC 60950, IEC60825-1,2

- RoHS compliant with RoHS 2.0(2015/863/EU)-amending.

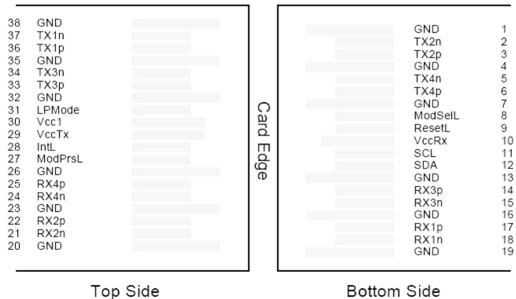

# Pin Descriptions

| Pin | Symbol  | Name                                                                              | Ref. |

|-----|---------|-----------------------------------------------------------------------------------|------|

| 1   | GND     | Ground                                                                            |      |

| 2   | Tx2n    | Transmitter Inverted Data Input, CML-I                                            |      |

| 3   | Tx2p    | Transmitter Non-Inverted Data output, CML-I                                       |      |

| 4   | GND     | Ground                                                                            |      |

| 5   | Tx4n    | Transmitter Inverted Data Input, CML-I                                            |      |

| 6   | Tx4p    | Transmitter Non-Inverted Data output, CML-I                                       |      |

| 7   | GND     | GND                                                                               |      |

|     |         | The ModSelL is an input pin. When held low by the host, the module responds       |      |

|     |         | to 2-wire serial communication commands. The ModSelL allows the use of            |      |

| 8   | ModSelL | multiple QSFP+ modules on asingle 2-wire interface bus. When the ModSelL          |      |

|     |         | is "High", the module shall not respond to or acknowledge any 2-wire interface    |      |

|     |         | communication from the host. ModSelL signal input node must be biased to          |      |

|     |         | the "High" state in the module                                                    |      |

|     |         | The ResetL pin must be pulled to Vcc in the QSFP+ module. A low level on the      |      |

|     |         | ResetL pin for longer than the minimum pulse length (t_Reset_init) initiates a    |      |

| 9   | ResetL  | complete module reset, returning all user module settings to their default state. |      |

|     |         | Module Reset Assert Time (t_init) starts on the rising edge after the low level   |      |

|     |         | on the ResetL pin is released.                                                    |      |

| 10  | VccRx   | + 3.3V Power Supply Receiver                                                      |      |

| 11  | SCL     | 2-Wire Serial Interface Clock                                                     |      |

| 12  | SDA     | 2-Wire Serial Interface Data                                                      |      |

| 13  | GND     | GND                                                                               |      |

| 14  | Rx3p    | Receiver Non-Inverted Data Output, CML-O                                          |      |

| 15  | Rx3n    | Receiver Inverted Data Output, CML-O                                              |      |

| 16  | GND     | GND                                                                               |      |

| 17  | Rx1p    | Receiver Non-Inverted Data Output, CML-O                                          |      |

| 18  | Rx1n    | Receiver Inverted Data Output, CML-O                                              |      |

| 19  | GND     | Ground                                                                            |      |

| 20  | GND     | Ground                                                                            |      |

| 21  | Rx2n    | Receiver Inverted Data Output, CML-O                                              |      |

| 22  | Rx2p    | Receiver Non-Inverted Data Output, CML-O                                          |      |

| 23  | GND     | Ground                                                                            |      |

| 24  | Rx4n    | Receiver Inverted Data Output, CML-O                                              |      |

| 25  | Rx4p    | Receiver Non-Inverted Data Output, CML-O                                          |      |

| 26  | GND     | Ground                                                                            |      |

| 27  | ModPrsL | Module Present, connect to GND                                                    |      |

# ΑΤϿΡ

| Pin | Symbol | Name                                                                                | Ref. |

|-----|--------|-------------------------------------------------------------------------------------|------|

|     |        | The IntL pin is an open collector output and must be pulled                         |      |

| 28  | IntL   | to host supply voltage on the host board. The INTL pin is de-asserted               |      |

| 20  | Inte   | "High" after completion of reset, when byte 2 bit 0 (Data Not Ready) is             |      |

|     |        | read with a value of '0' and the flag field is read.                                |      |

| 29  | VccTx  | +3.3 V Power Supply transmitter                                                     |      |

| 30  | Vcc1   | +3.3 V Power Supply                                                                 |      |

|     |        | The LPMode pin shall be pulled up to Vcc in the QSFP+ module.                       |      |

| 31  | LPMode | This function is affected by the LPMode pin and the combination of the              |      |

|     |        | Power_over-ride and Power_set softwarecontrol bits (Address A0h, byte 93 bits 0,1). |      |

| 32  | GND    | Ground                                                                              |      |

| 33  | Тх3р   | Transmitter Non-Inverted Data Input, CML-I                                          |      |

| 34  | Tx3n   | Transmitter Inverted Data Output, CML-I                                             |      |

| 35  | GND    | Ground                                                                              |      |

| 36  | Tx1p   | Transmitter Non-Inverted Data Input, CML-I                                          |      |

| 37  | Tx1n   | Transmitter Inverted Data Output, CML-I                                             |      |

| 38  | GND    | Ground                                                                              |      |

Viewed from Top

Bottom Side Viewed from Bottom

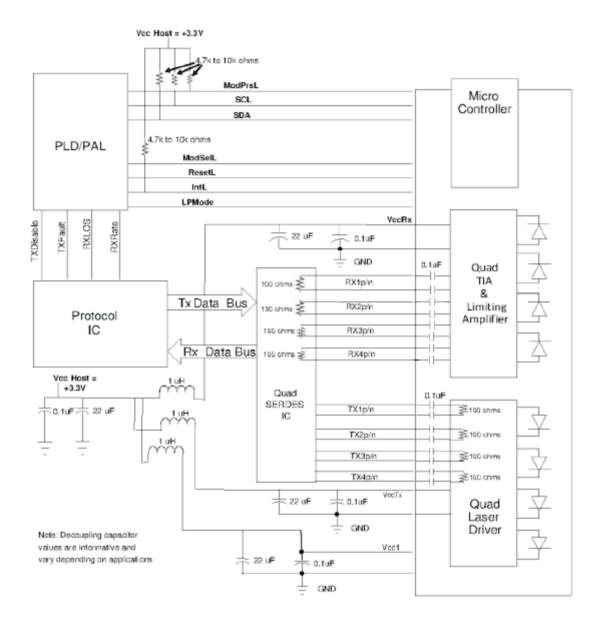

#### **Recommend Circuit Schematic**

## Absolute Maximum Ratings

|                           | rmbol | Min | Тур | Max   | Unit | Ref. |

|---------------------------|-------|-----|-----|-------|------|------|

| Maximum Supply Voltage Vc | .c -0 | 0.5 | +-  | 4.0 V | /    |      |

| Storage Temperature TS    | , -4  | 40  | +   | 85    | °C   |      |

| Operating Humidity RH     | Η (   | 0   | 8   | 35    | %    |      |

# **Recommended Operating Conditions**

| Parameter                  | Symbol | Min  | Тур   | Max  | Unit | Ref.       |

|----------------------------|--------|------|-------|------|------|------------|

| Power Supply Voltage       | Vcc    | 3.13 | 3.30  | 3.47 | V    |            |

| Power Supply Current       | lcc    | -    | -     | 1.36 | А    | Commercial |

| Case Operating Temperature | Tc     | 0    | -     | +70  | °C   | Commercial |

| Bit Rate Each Lane         | Br     |      | 25.78 |      | Gbps |            |

| 9/125um G.652 SMF          | Lmax   | -    | -     | 10   | km   |            |

#### **Electrical Characteristics**

| Parameter                      | Symbol   | Min     | Тур | Max     | Unit | Ref. |

|--------------------------------|----------|---------|-----|---------|------|------|

| Transmitter                    |          |         |     |         |      |      |

| Input differential impedance   | Rin      | 90      | 100 | 110     | Ω    | 1    |

| Differential data input swing  | Vin, pp  | 95      | -   | 900     | mV   |      |

| TX Disable-High                | -        | Vcc-0.8 | -   | Vcc     | V    |      |

| TX Disable-Low                 | -        | Vee     | -   | Vee+0.8 | V    |      |

| TX Fault-High                  | -        | Vcc-0.8 | -   | Vcc     | V    |      |

| TX Fault-Low                   | -        | Vee     | -   | Vee+0.8 | V    |      |

| Receiver                       |          |         |     |         |      |      |

| Output Differential Impedance  | Rin      | 90      | 100 | 110     | Ω    | 1    |

| Differential Data Output Swing | Vout, pp | -       | -   | 900     | mV   | 2    |

| LOS-High                       | -        | Vcc-0.8 |     | Vcc     | V    |      |

| LOS-Low                        | -        | Vee     |     | Vee+0.8 | V    |      |

#### Notes:

1. AC coupled.

2. Into 100 ohm differential termination.

### **Optical Characteristics**

| Parameter                                  | Symbol | Min     | Тур     | Max     | Unit | Ref. |

|--------------------------------------------|--------|---------|---------|---------|------|------|

| Transmitter                                |        |         |         |         |      |      |

| Total Average Launch Power                 | РТ     |         |         | 10.5    | dBm  |      |

| Average Launch Power, each Lane            |        | -4.3    |         | 4.5     | dBm  |      |

| Optical Modulation Amplitude, each Lane    | OMA    | -1.3    |         | +4.5    | dBm  |      |

|                                            | LO     | 1294.53 | 1295.56 | 1296.59 | nm   |      |

| Optical Wavelength                         | L1     | 1299.02 | 1300.05 | 1301.09 | nm   |      |

| optical Navelength                         | L2     | 1303.54 | 1304.58 | 1305.63 | nm   |      |

|                                            | L3     | 1308.09 | 1309.14 | 1310.19 | nm   |      |

| Side-mode Suppression Ratio                | SMSR   | 30      |         |         | dB   |      |

| Extinction Ratio                           | ER     | 4       |         |         | dB   |      |

| Receiver                                   |        |         |         |         |      |      |

| RX Sensitivity @25.78 Gb/s, each lane      | SENS   | -       | -       | -10.6   | dBm  | 1,2  |

| RX Sensitivity(OMA) @25.78 Gb/s, each lane | SENS   | -       | -       | -8.6    | dBm  | 2    |

| Receiver Overload                          |        | 4.5     | -       | -       | dBm  |      |

| LOS De-Assert                              | LOSD   | -       | -       | -12     | dBm  |      |

| LOS Assert                                 | LOSA   | -25     | -       | -       | dBm  |      |

| LOS Hysteresis                             | -      | 0.5     | -       | -       | dB   |      |

Notes:

1. This value is informative and not the principal indicator of signal strength. A received power below this

value cannot be compliant; however, a value above this does not ensure compliance.

2. Measured with PRBS 2<sup>31</sup>-1 at 1E-12 BER.

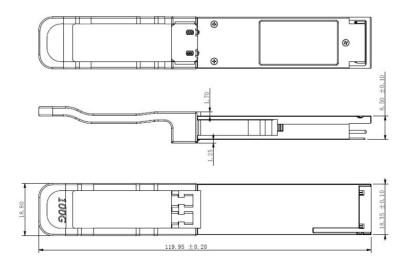

## Mechanical Specifications

APQP2LRACDL10A

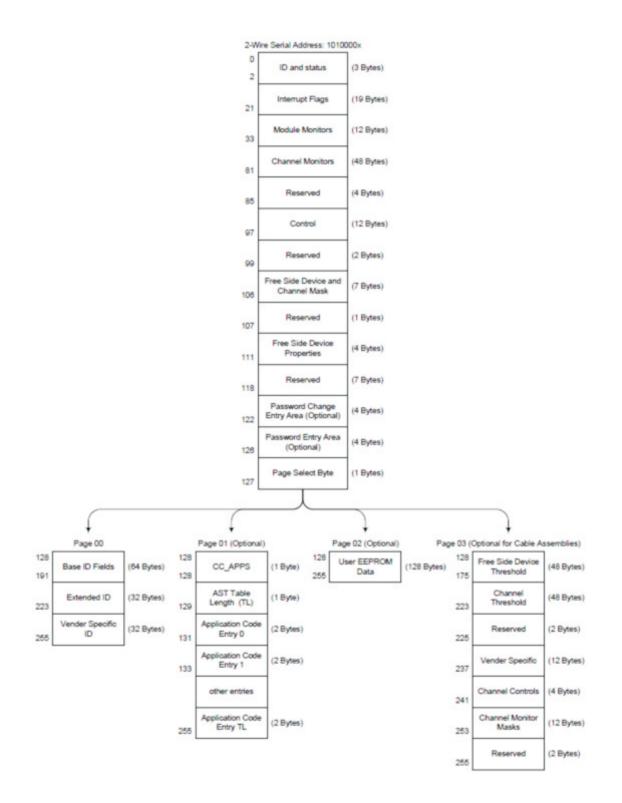

#### **EEPROM Information**

• EEPROM memory map specific data field description is as below:

#### Digital Diagnostic Monitoring Interface

Five transceiver parameter values are monitored. The following table defines the monitory parameter's accuracy.

| Parameter    | Range          | Accuracy | Calibration |

|--------------|----------------|----------|-------------|

| Temperature  | 0 to +70°C     | ±3°C     | Internal    |

| Voltage      | 2.97 to 3.63V  | ±3%      | Internal    |

| Bias Current | 0 to 100mA     | ±10%     | Internal    |

| TX Power     | -4.3 to 4.5dBm | ±3dB     | Internal    |

| RX Power     | -11 to 4.5dBm  | ±3dB     | Internal    |

## **Revision History**

| Revision   | Initiated   | Reviewed     | Approved  | DCN                                                        | Release Date |

|------------|-------------|--------------|-----------|------------------------------------------------------------|--------------|

| Version1.0 | Colin Huang | Billy Tang   | Dingzheng | New Released.                                              | Apr 21, 2019 |

| Version1.1 | Billy Tang  | Colin Huang  | Dingzheng | Update the new template.                                   | Dec 19, 2019 |

| Version1.2 | Tang Rong   | Qiu Shaofeng | Dingzheng | Add TX Power Digital Diagnostic<br>Monitoring Information. | Jul 27, 2021 |

let's make it personal